#### ISL8215M

15A 42V Single-Channel DC/DC Step-Down Power Module

FN8878 Rev.1.00 Aug 30, 2017

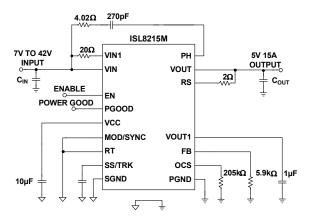

The <u>ISL8215M</u> power module is a single-channel, synchronous step-down, non-isolated complete power supply, capable of delivering up to 15A of continuous current. Operating from a single 7V to 42V wide input power rail and integrating the controller, power inductor, and MOSFETs, the ISL8215M requires only a few external components to operate and is optimized for space constrained applications.

Based on a valley current mode PWM control scheme, the ISL8215M provides fast transient response and excellent loop stability. It offers an adjustable output voltage range of 0.6V to 12V with better than 1.5% accuracy over line, load, and temperature. A 40ns typical minimum on time and an adjustable operating frequency allow it to support low duty cycle, single-step down conversions to point-of-load voltages and its operating frequency can also be synchronized with an external clock signal. The ISL8215M implements a selectable Pulse Skipping Mode (PSM) with Diode Emulation Mode (DEM) to improve light-load efficiency for battery related applications. A programmable soft-start reduces the inrush current from the input supply while a dedicated enable pin and power-good flag allow for easy system power rails sequencing with voltage tracking capability. Excellent efficiency and low thermal resistance permit full power operation without heatsinks.

Input Undervoltage Lockout (UVLO), over-temperature, programmable overcurrent, output overvoltage, and output prebias start-up protections ensure safe operations under abnormal operating conditions.

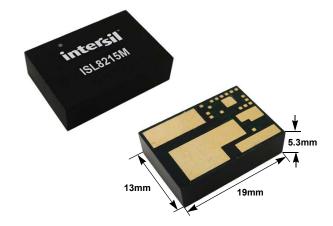

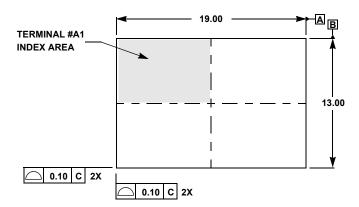

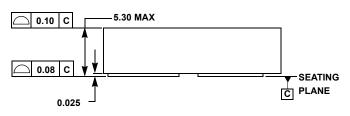

The ISL8215M is available in a compact RoHS compliant thermally-enhanced 19mmx13mmx5.3mm HDA package.

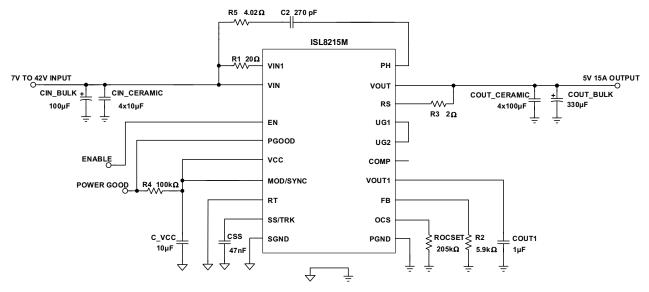

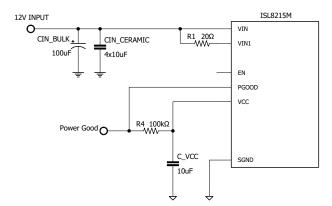

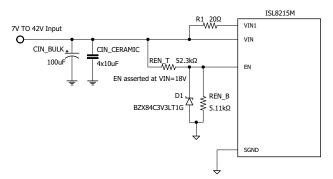

**Figure 1. Typical Application Circuit**

#### Features

- 15A single-channel complete power supply

- Integrates controller, MOSFETs, and inductor

- 7V to 42V wide input voltage range

- Adjustable output voltage

- 0.6V to 12V wide output voltage range

- 40ns on-time low duty cycle conversion capable

- ±1.5% accuracy over line, load, and temperature

- Up to 96.5% efficiency

- 300kHz to 2MHz adjustable PWM operations

- External synchronization up to 1MHz

- Selectable light-load PSM/DEM efficiency mode

- Enable pin and power-good flag

- Programmable soft-start or voltage tracking

- Complete protection

- UVLO, programmable overcurrent, overvoltage, and over-temperature

- Prebias output start-up

- 19mm x 13mm x 5.3mm HDA package

#### **Applications**

- · Industrial and medical equipment

- Aftermarket automotive

- Telecom and datacom equipment

#### Related Literature

- For a full list of related documents, visit our website

- ISL8215M product page

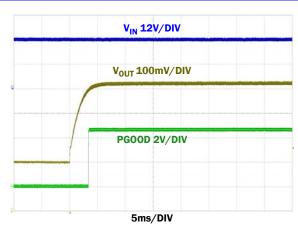

Figure 2. V<sub>IN</sub> = 24V

Page 1 of 41

# **Table of Contents**

| 1.  | Overview                            | 4    |

|-----|-------------------------------------|------|

| 1.1 | Typical Application Circuits        | 4    |

| 1.2 | Block Diagram                       | 6    |

| 1.3 | Ordering Information                | 6    |

| 1.4 | Pin Configuration                   | 7    |

| 1.5 | Pin Descriptions                    | 7    |

| 2.  | Specifications                      | . 10 |

| 2.1 | Absolute Maximum Ratings            | . 10 |

| 2.2 | Thermal Information                 | . 10 |

| 2.3 | Recommended Operating Conditions    | . 10 |

| 2.4 | Electrical Specifications           | . 11 |

| 3.  | Typical Performance Curves          | . 14 |

| 3.1 | Efficiency Performance              | . 14 |

| 3.2 | Output Voltage Ripple               | . 15 |

| 3.3 | Load Transient Response Performance | . 16 |

| 3.4 | Start-Up Waveforms                  | . 17 |

| 3.5 | Derating                            | . 17 |

| 4.  | Functional Description              | . 19 |

| 4.1 | Power-Good Indicator                | . 19 |

| 4.2 | Self-Enable Operation               | . 19 |

| 4.3 | Enable                              | . 19 |

| 4.4 | Prebiased Power-Up                  | . 19 |

| 4.5 | PWM/CCM Mode                        | . 20 |

| 4.6 | PSM/DEM Light-Load Efficiency Mode  | . 20 |

| 4.7 | Internal 5V Linear Regulator (VCC)  | . 20 |

| 4.8 | Gate Control Logic Optimization     | . 20 |

| 5.  | Application Information             | . 21 |

| 5.1 | Output Voltage Programming          | . 21 |

| 5.2 | Switching Frequency Selection       | . 21 |

| 5.3 | External Frequency Synchronization  | . 22 |

| 5.4 | Soft-Start Operation                | . 22 |

| 5.5 | Tracking Operation                  | . 23 |

| 5.6 | Input Voltage Range                 |      |

| 5.7 | Input Capacitor Selection           |      |

| 5.8 | Output Capacitor Selection          | . 25 |

| 6.  | Protection Circuits                 | . 26 |

| 6.1 | Undervoltage Lockout                | . 26 |

| 6.2 | Overcurrent Protection              | . 26 |

| 6.3 | Overvoltage Protection              | . 27 |

| 6.4 | Over-Temperature Protection         | . 27 |

#### ISL8215M

|     | Layout Guidelines         |      |

|-----|---------------------------|------|

| 7.1 | Layout Considerations     | . 28 |

| 8.  | Thermal Considerations    | . 30 |

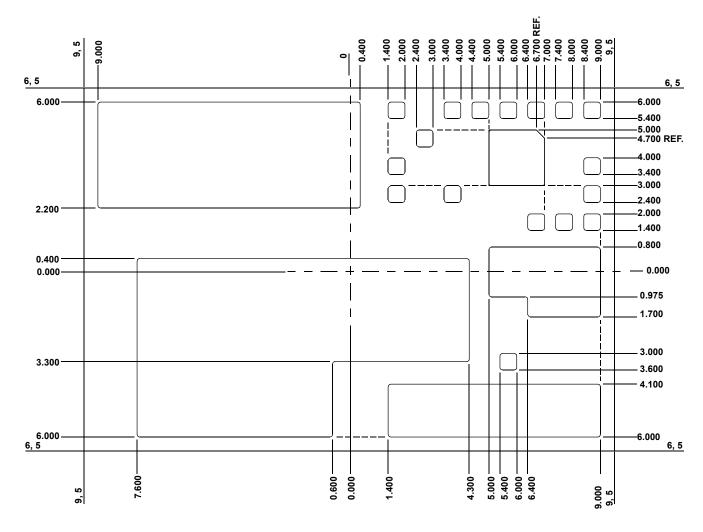

| 9.  | Package Description       | . 31 |

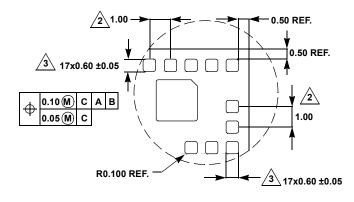

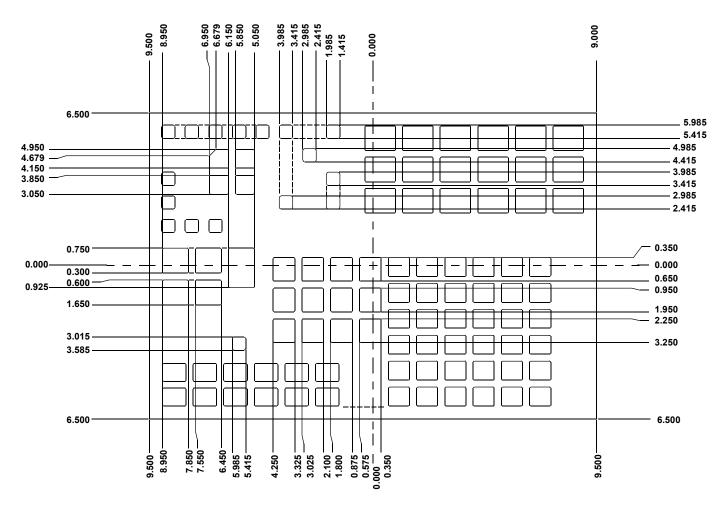

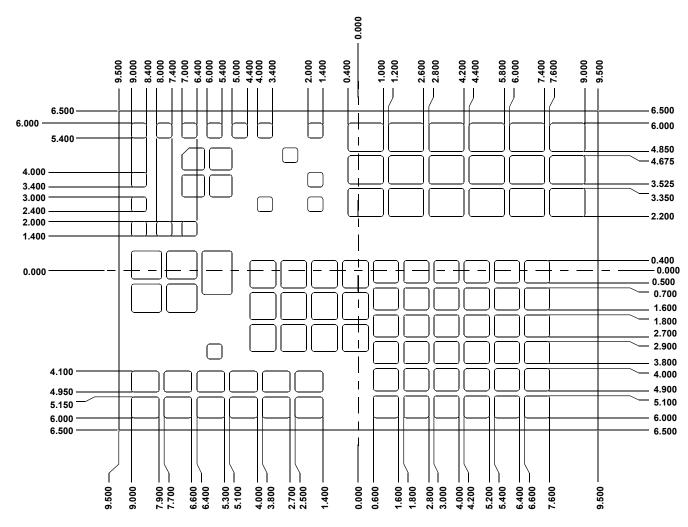

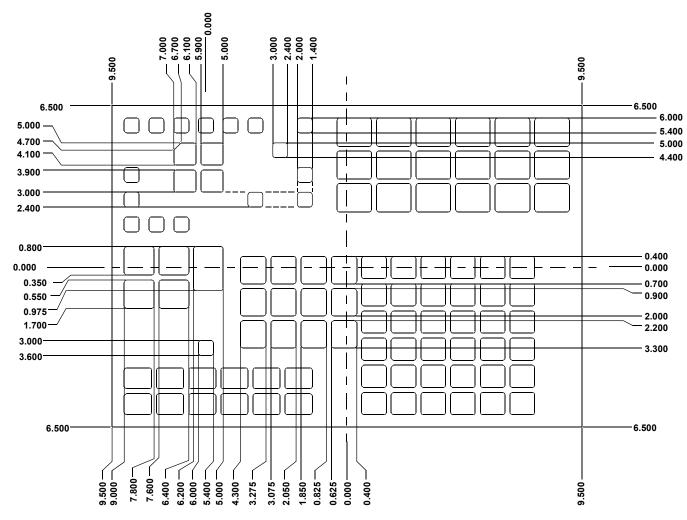

| 9.1 | PCB Layout Pattern Design | . 31 |

| 9.2 | Thermal Vias              |      |

| 9.3 | Stencil Pattern Design    | . 31 |

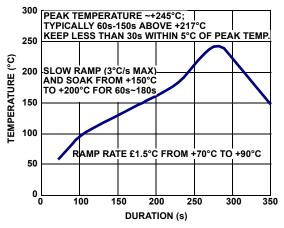

| 9.4 | Reflow Parameters         | . 32 |

| 10. | Revision History          | . 33 |

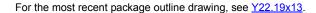

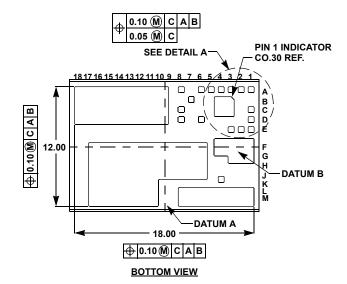

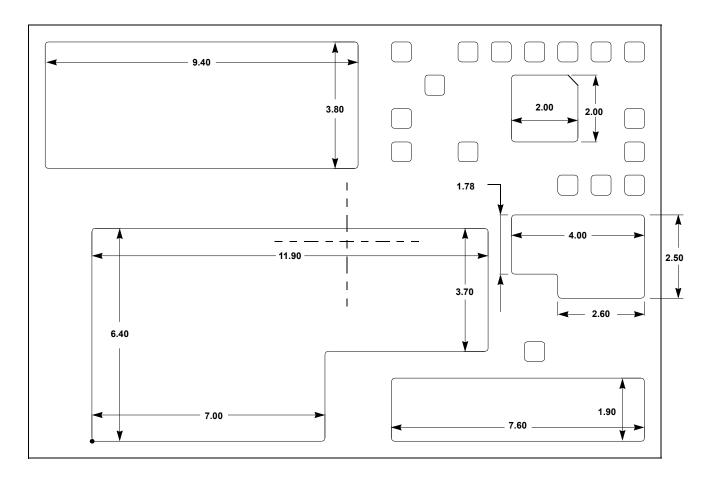

| 11. | Package Outline Drawing   | . 34 |

| 12  | About Intersil            | 41   |

#### 1. **Overview**

#### **Typical Application Circuits** 1.1

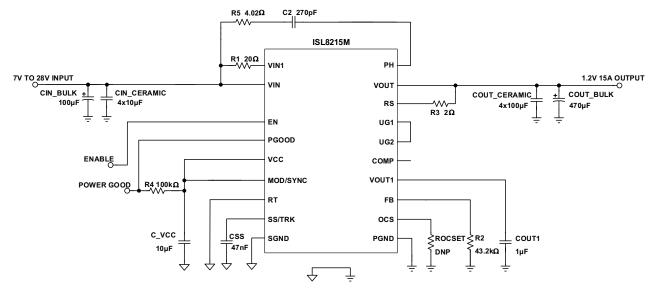

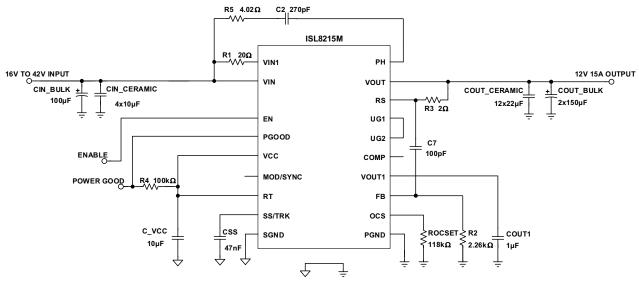

Figure 3.  $V_{OUT} = 1.2V$ ,  $f_{SW} = 300$ kHz, Light-Load Mode,  $t_{SS} = 15$ ms

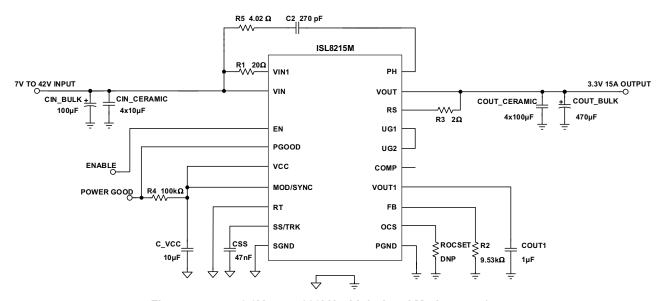

Figure 4.  $V_{OUT}$  = 3.3V,  $f_{SW}$  = 300kHz, Light-Load Mode,  $t_{SS}$  = 15ms

Figure 5.  $V_{OUT}$  = 5V,  $f_{SW}$  = 300kHz, Light-Load Mode,  $t_{SS}$  = 15ms

Figure 6.  $V_{OUT}$  = 12V,  $f_{SW}$  = 600kHz, PWM Only,  $t_{SS}$  = 15ms

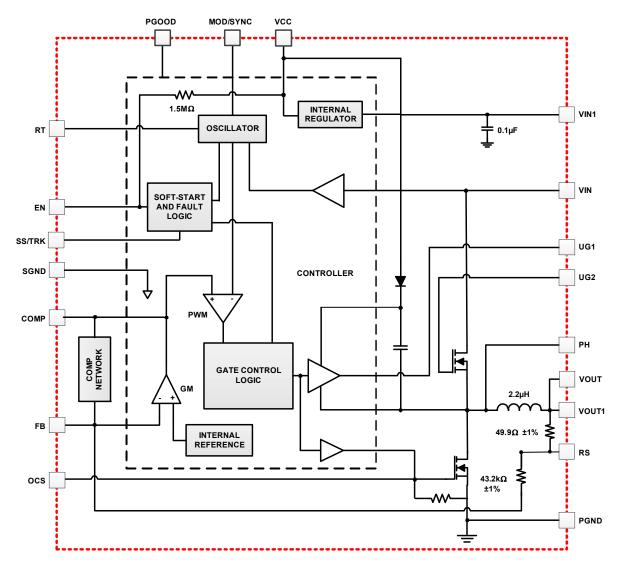

## 1.2 Block Diagram

Figure 7. Block Diagram

# 1.3 Ordering Information

| Part Number<br>( <u>Notes 1, 2, 3</u> ) | Part<br>Marking  | Temp. Range<br>(°C) | Package<br>(RoHS Compliant) | Pkg.<br>Dwg. # |  |

|-----------------------------------------|------------------|---------------------|-----------------------------|----------------|--|

| ISL8215MIRZ                             | ISL8215M         | -40 to +125         | 19x13 HDA                   | Y22.19x13      |  |

| ISL8215MEVAL1Z                          | Evaluation Board |                     |                             |                |  |

#### Notes:

- 1. Add "-T" suffix for 350 unit or "-T1" suffix for 100 unit tape and reel options. Refer to TB347 for details on reel specifications.

- These Intersil plastic packaged products are RoHS compliant by EU exemption 7C-I and employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish which is compatible with both SnPb and Pb-free soldering operations. Intersil RoHS compliant products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), see product information page for <a href="ISL8215M">ISL8215M</a>. For information on Moisture Sensitivity Level (MSL), see <a href="IB363">TB363</a>.

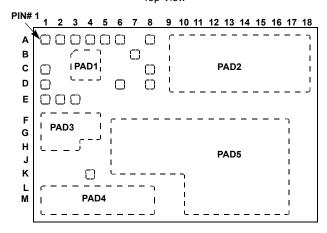

# 1.4 Pin Configuration

ISL8215M (22 Ld 19x13 HDA) Top View

## 1.5 Pin Descriptions

| Pin<br>Number | Pin<br>Name | Function                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAD1          | SGND        | Signal ground. The small-signal ground is common to all control circuitry and all voltage levels are measured with respect to this pin. SGND should be tied to a solid low noise GND plane. See <u>"Layout Considerations" on page 28</u> and <u>Figure 48 on page 29</u> for details.                                                                                                       |

| PAD2          | VOUT        | Regulated power supply output. Output load should be applied between this pin and PGND. An external resistor on the FB pin sets the output voltage in a range of 0.6V to 12V. Refer to derating curves for maximum load current at various output voltage.                                                                                                                                   |

| PAD3          | PGND        | Power ground. This pin is connected to the source of the lower MOSFET inside the module and should be connected to the (-) terminals of the external input capacitors and output capacitors.                                                                                                                                                                                                 |

| PAD4          | VIN         | Power input. This pin should be connected directly to an input rail in a range of 7V to 42V. Input ceramic capacitors should be connected between this pin and PGND as close as possible to the device.                                                                                                                                                                                      |

| PAD5          | PH          | Phase node connection. This pin is connected to the junction of the high-side MOSFET's source, output filter inductor, and low-side MOSFET's drain. For a switching frequency of 300kHz and a 42V input, a 4.02Ω 1206 resistor and a 270pF X7R 100V 0603 capacitor in series from PH to VIN (see Figures 3 through 6) are required. Refer to "Layout Considerations" on page 28 for details. |

| A1            | COMP        | Voltage error amplifier output. Internal compensation networks are implemented to stabilize the system and achieve optimal transient response across the full range of input and output operating conditions. Leave this pin floating.                                                                                                                                                       |

| A2            | SS/TRK      | Soft-start/tracking pin. Connecting a capacitor from this pin to signal ground sets the soft-start output voltage ramp rate. For tracking control, an external supply rail applied to this pin via a resistor divider will be tracked by the output voltage. Leave this pin floating to enable a soft-start time of 1.5ms. Refer to "Tracking Operation" on page 23.                         |

| А3            | RT          | Switching frequency selection. Connect to SGND to set the operating frequency to 300kHz. Connect to VCC or float this pin to set the operating frequency to 600kHz. Connect a resistor from RT to SGND to program the switching frequency. Refer to the "Switching Frequency Selection" on page 21.                                                                                          |

| A4            | PGOOD       | Open-drain, power-good output. PGOOD signal is asserted when the output voltage is within ±12.5% of the nominal set output voltage and de-asserted when the output voltage is outside of the stated range or the EN pin is pulled low.                                                                                                                                                       |

| Pin    | Pin      | <b>-</b>                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Name     | Function                                                                                                                                                                                                                                                                                                                                                                                        |

| A5     | MOD/SYNC | Light-load mode selection/synchronization input.  Connect to VCC to enable light load PSM/DEM mode with pulse skipping at light loads.  Connect to SGND or leave floating to enable constant frequency PWM only mode.  Connect to external clock to synchronize the internal switching operations to an external clock; PWM mode only.                                                          |

| A6, A8 | EN       | Enable inputs.  Connect to logic high level or left floating to enable the device. An internal pull-up resistor allows for self enable operations upon application of VIN.  Connect to logic low level or SGND: Disables the device.  These two pins should be connected together externally through a PCB trace.                                                                               |

| В7     | VIN1     | This pin should be tied to the input rail through a $20\Omega$ 0603 resistor. It provides power to the internal linear drive circuitry and is also used by the feed-forward controller to adjust the amplitude of the PWM sawtooth.                                                                                                                                                             |

| C1     | FB       | Feedback input. Connect a resistor between this pin and SGND to adjust the output voltage. Refer to <u>"Output Voltage Programming" on page 21.</u>                                                                                                                                                                                                                                             |

| D1     | RS       | Output voltage remote sense feedback. Connect to the positive output regulation point. To achieve best regulation performance, connect a $2\Omega$ resistor between the RS pin and the point of load. An internal $49.9\Omega$ resistor connected between the RS pin and the VOUT1 pin can be used for injecting a small signal for loop gain measurements.                                     |

| D6     | UG1      | High-side MOSFET gate driver output. Connect this pin to UG2, externally through a PCB trace.                                                                                                                                                                                                                                                                                                   |

| K4     | UG2      | Pin connected to the gate of high-side MOSFET. Connect this pin to UG1 externally through a PCB trace.                                                                                                                                                                                                                                                                                          |

| E1     | VOUT1    | Power supply output. Connect a 1µF ceramic decoupling capacitor between this pin and SGND.                                                                                                                                                                                                                                                                                                      |

| E2     | ocs      | Low-side MOSFET gate driver output and OC set pin. Resistor between this pin and ground is used to set the overcurrent threshold. Inside the module, a 26.1k resistor is connected between this pin and SGND. An external resistor in parallel with the internal 26.1k resistor can be used to reduce the overcurrent threshold. Refer to "Overcurrent Protection" on page 26 for more details. |

| E3     | VCC      | 5V internal linear regulator output. This output supplies bias for the IC, the low-side gate driver and the internal boot circuitry for the high-side gate driver. Decouple with a 10μF ceramic capacitor placed close to the pin to power ground. Do not allow the voltage at VCC to exceed VIN at any time.                                                                                   |

| C8     | NC       | No connection pin. Do not connect these pins.                                                                                                                                                                                                                                                                                                                                                   |

| D8     | NC       |                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 1. ISL8215M Design Guide Matrix (Refer to Figures 3 Through 6)

| Case | V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | R2<br>(kΩ) | C <sub>IN</sub><br>(Bulk)<br>(µF) | C <sub>IN</sub><br>(Ceramic)<br>(μF) | C <sub>OUT</sub><br>(Bulk)<br>(μF) | C <sub>OUT</sub><br>(Ceramic)<br>(µF) | Freq<br>(kHz) | RT<br>Config | ROCSET (kΩ) | C <sub>7</sub> (pF) | R5<br>(Package)<br>( <u>Note 4</u> ) |

|------|---------------------|----------------------|------------|-----------------------------------|--------------------------------------|------------------------------------|---------------------------------------|---------------|--------------|-------------|---------------------|--------------------------------------|

| 1    | 12                  | 0.8                  | 130        | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 2    | 12                  | 0.9                  | 86.6       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 3    | 12                  | 1                    | 64.9       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 4    | 12                  | 1.2                  | 43.2       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 5    | 12                  | 1.8                  | 21.5       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 6    | 12                  | 2.5                  | 13.7       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 7    | 12                  | 3.3                  | 9.65       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0402                                 |

| 8    | 12                  | 5                    | 5.90       | 1x100                             | 4x10                                 | 1x330                              | 4x100                                 | 300           | SGND         | 205         | Open                | 0402                                 |

| 9    | 24                  | 0.9                  | 86.6       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 10   | 24                  | 1                    | 64.9       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 11   | 24                  | 1.2                  | 43.2       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 12   | 24                  | 1.8                  | 21.5       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 13   | 24                  | 2.5                  | 13.7       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 14   | 24                  | 3.3                  | 9.65       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 0603                                 |

| 19   | 24                  | 5                    | 5.90       | 1x100                             | 4x10                                 | 1x330                              | 4x100                                 | 300           | SGND         | 205         | Open                | 0603                                 |

| 20   | 7 to 42             | 1.5                  | 28.7       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 1206                                 |

| 21   | 7 to 42             | 1.8                  | 21.5       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 1206                                 |

| 22   | 7 to 42             | 2.5                  | 13.7       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 1206                                 |

| 23   | 7 to 42             | 3.3                  | 9.65       | 1x100                             | 4x10                                 | 1x470                              | 4x100                                 | 300           | SGND         | DNP         | Open                | 1206                                 |

| 24   | 7 to 42             | 5                    | 5.90       | 1x100                             | 4x10                                 | 1x330                              | 4x100                                 | 300           | SGND         | 205         | Open                | 1206                                 |

| 27   | 16 to 42            | 12                   | 2.26       | 1x100                             | 4x10                                 | 2x150                              | 12x22                                 | 600           | Open         | 118         | 100                 | 1210                                 |

Note:

Table 2. Recommended Input/Output Capacitor

| Vendor                       | Value            | Part Number        |  |  |

|------------------------------|------------------|--------------------|--|--|

| Murata, Output Ceramic       | 100μF, 10V, 1210 | GRM32ER61A107ME20L |  |  |

| Murata, Output Ceramic       | 22µF, 16V, 1210  | GRM32ER71C226KE18L |  |  |

| Murata, Input Ceramic        | 10μF, 50V, 1210  | GRM32ER71H106KA12L |  |  |

| Panasonic, Output Bulk       | 470μF, 6.3V      | 6TPF470MAH         |  |  |

| Panasonic, Output Bulk       | 330μF, 6.3V      | 6TPF330M9L         |  |  |

| Panasonic, Output Bulk       | 150μF, 16V       | 16TQC150MYF        |  |  |

| United Chemi-Con, Input Bulk | 100μF, 50V       | EMZA500ADA101MHA0G |  |  |

| Murata                       | 270pF, 100V, X7R | GRM188R72A271KA01D |  |  |

<sup>4.</sup> Refer to "Layout Considerations" on page 28 for more details about package selection size for R5.

# 2. Specifications

## 2.1 Absolute Maximum Ratings

| Parameter                                                | Minimum | Maximum               | Unit |

|----------------------------------------------------------|---------|-----------------------|------|

| VCC to SGND                                              | -0.3    | +5.9                  | V    |

| VIN to PGND                                              | -0.3    | +45                   | V    |

| VIN1 to PGND                                             | -0.3    | +45                   | V    |

| EN, PGOOD, SS/TRK, FB, COMP to SGND                      | -0.3    | V <sub>CC</sub> + 0.3 | V    |

| VOUT to PGND                                             | -0.3    | 16                    | V    |

| VOUT1 to PGND                                            | -0.3    | 16                    | V    |

| RS to PGND                                               | -0.3    | 16                    | V    |

| UG1 to PHASE                                             | -0.3    | V <sub>CC</sub> + 0.3 | V    |

| UG2 to PHASE                                             | -20     | +20                   | V    |

| OCS to SGND                                              | -0.3    | V <sub>CC</sub> + 0.3 | V    |

| RT, MOD/SYNC to SGND                                     | -0.3    | V <sub>CC</sub> + 0.3 | V    |

| ESD Rating                                               | Va      | lue                   | Unit |

| Human Body Model (Tested per JS-001-2014)                | 2       |                       | kV   |

| Machine Model (Tested per JESD22-A115C)                  | 200     |                       | V    |

| Charged Device Model (Tested per JS-002-2014)            | 7       | 50                    | V    |

| Latch-Up (Tested per JESD78E; Class II, Level A, +125°C) | 1       | 00                    | mA   |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### 2.2 Thermal Information

| Thermal Resistance (Typical)   | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |  |  |

|--------------------------------|------------------------|------------------------|--|--|

| 22 Ld HDA Package (Notes 5, 6) | 11.7                   | 1.9                    |  |  |

Notes:

θ<sub>JA</sub> is measured in free air with the module mounted on a 4-layer thermal test board 4.5x3 inch in size with significant coverage of 2.8oz Cu on top and bottom and 2oz Cu on buried plane layers, with numerous vias.

6. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is the center of the package underside.

| Parameter                 | Minimum        | Maximum | Unit |

|---------------------------|----------------|---------|------|

| Storage Temperature Range | -65            | +150    | °C   |

| Pb-Free Reflow Profile    | Refer to TB493 |         |      |

# 2.3 Recommended Operating Conditions

| Parameter                                  | Minimum | Maximum | Unit |

|--------------------------------------------|---------|---------|------|

| V <sub>IN</sub> to GND                     | 7       | 42      | V    |

| Output Voltage, V <sub>OUT</sub>           | 0.6     | 12      | V    |

| Junction Temperature Range, T <sub>J</sub> | -40     | +125    | °C   |

# 2.4 Electrical Specifications

Unless otherwise noted, typical specifications are measured at  $V_{IN}$  = 7V to 42V,  $V_{OUT}$  = 1.2V,  $C_{L}V_{CC}$  = 10 $\mu$ F,  $T_{A}$  = +25°C. Boldface limits apply across the internal junction temperature range, -40°C to +125°C.

| Parameter                              | Symbol                                  | Test Conditions                                                                                                                                                       | Min<br>(Note 9) | Тур  | Max<br>(Note 9) | Unit              |

|----------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------------------|

| V <sub>IN</sub> Supply                 |                                         |                                                                                                                                                                       | •               |      | •               |                   |

| Input Voltage Range                    | V <sub>IN</sub>                         |                                                                                                                                                                       | 7               |      | 42              | V                 |

| Controller Input Current               |                                         |                                                                                                                                                                       | •               |      |                 |                   |

| Shutdown Current (Note 7)              | I <sub>VIN1Q</sub>                      | EN = 0<br>PGOOD is floating<br>V <sub>IN1</sub> = 12V                                                                                                                 |                 | 5    | 10              | μA                |

| Operating Current (Note 8)             | I <sub>VIN1OP</sub>                     | PGOOD is floating<br>V <sub>IN1</sub> = 12V                                                                                                                           |                 | 2.5  | 4               | mA                |

| V <sub>CC</sub> Supply (Note 7)        |                                         |                                                                                                                                                                       |                 |      |                 |                   |

| Internal LDO Output Voltage            | V <sub>CC</sub>                         | V <sub>IN</sub> = 12V, I <sub>L</sub> = 0mA                                                                                                                           | 4.85            | 5.10 | 5.40            | V                 |

|                                        |                                         | V <sub>IN</sub> > 7V, I <sub>L</sub> = 75mA                                                                                                                           | 4.75            | 5.05 |                 | V                 |

| Maximum Supply Current of Internal LDO | I <sub>VCC_MAX</sub>                    | V <sub>VCC</sub> = 0V, V <sub>IN</sub> = 12V                                                                                                                          |                 | 120  |                 | mA                |

| Output Regulation                      | _                                       |                                                                                                                                                                       | 1               |      | I               |                   |

| Output Continuous Current Range        | I <sub>OUT</sub>                        |                                                                                                                                                                       | 0               |      | 15              | Α                 |

| Output Voltage Range (Note 13)         | V <sub>OUT_RANGE</sub>                  |                                                                                                                                                                       | 0.6             |      | 12.0            | V                 |

| Output Voltage Set-Point Accuracy      | V <sub>OUT_ACCY</sub>                   | Total variation with line, load, and temperature (-40°C $\leq$ T <sub>J</sub> $\leq$ +125°C)                                                                          | -1.5            |      | 1.5             | %                 |

| Line Regulation                        | ΔV <sub>OUT/</sub> V <sub>OUT_SET</sub> | V <sub>IN</sub> from 7V to 42V, I <sub>OUT</sub> = 0A to 15A                                                                                                          |                 | 0.1  |                 | %                 |

| Load Regulation                        | ΔV <sub>OUT/</sub> V <sub>OUT_SET</sub> | From 0A to 15A, V <sub>IN</sub> = 7V to 42V                                                                                                                           |                 | 0.3  |                 | %                 |

| Output Ripple Voltage                  | V <sub>OUT(AC)</sub>                    | V <sub>IN</sub> = 24V, V <sub>OUT</sub> = 1.2V, I <sub>OUT</sub> = 15A,<br>4x100μF ceramic capacitor and<br>1x470μF POSCAP                                            |                 | 13   |                 | mV <sub>P-P</sub> |

| Dynamic Characteristics                |                                         |                                                                                                                                                                       |                 |      | <u> </u>        |                   |

| Voltage Change of Positive Load Step   | V <sub>OUT_DP</sub>                     | Current slew rate = $2.5A/\mu s$ ,<br>$V_{IN}$ = $24V$ , $4x100\mu F$ ceramic<br>capacitor and $1x470\mu F$ POSCAP<br>$V_{OUT}$ = $1.2V$ , $I_{OUT}$ = $0A$ to $7.5A$ |                 | 60   |                 | mV                |

| Voltage Change of Negative Load Step   | V <sub>OUT_DN</sub>                     | Current slew rate = $2.5A/\mu s$ ,<br>$V_{IN}$ = $24V$ , $4x100\mu F$ ceramic<br>capacitor and $1x470\mu F$ POSCAP<br>$V_{OUT}$ = $1.2V$ , $I_{OUT}$ = $7.5A$ to $0A$ |                 | 60   |                 | mV                |

| Undervoltage Lockout                   |                                         |                                                                                                                                                                       |                 |      |                 |                   |

| Undervoltage Lockout, Rising           | V <sub>UVLOTHR</sub>                    | V <sub>IN</sub> voltage, 0mA on V <sub>CC</sub>                                                                                                                       | 3.70            | 3.90 | 4.20            | V                 |

| Undervoltage Lockout, Falling          | V <sub>UVLOTHF</sub>                    | V <sub>IN</sub> voltage, 0mA on V <sub>CC</sub>                                                                                                                       | 3.35            | 3.50 | 3.85            | V                 |

| EN Threshold                           |                                         |                                                                                                                                                                       |                 |      |                 |                   |

| EN Rise Threshold                      | V <sub>ENSS_THR</sub>                   | V <sub>IN</sub> = 12V                                                                                                                                                 | 1.25            | 1.60 | 1.95            | V                 |

| EN Fall Threshold                      | V <sub>ENSS_THF</sub>                   | V <sub>IN</sub> = 12V                                                                                                                                                 | 1.05            | 1.25 | 1.55            | V                 |

| EN Hysteresis                          | V <sub>ENSS_HYST</sub>                  | V <sub>IN</sub> = 12V                                                                                                                                                 | 180             | 350  | 500             | mV                |

| Soft-Start Current                     | •                                       | •                                                                                                                                                                     | •               |      | •               |                   |

| SS/TRK Soft-Start Charge Current       | I <sub>SS</sub>                         | SS/TRK = 0V                                                                                                                                                           |                 | 2    |                 | μΑ                |

| Default Internal Minimum Soft-starting |                                         | ı                                                                                                                                                                     |                 |      |                 |                   |

| Default Internal Output Ramping Time   | t <sub>SS_MIN</sub>                     | SS/TRK open                                                                                                                                                           |                 | 1.5  |                 | ms                |

| Power-Good Monitors                    |                                         | 1                                                                                                                                                                     | 1               |      | I.              | 1                 |

Unless otherwise noted, typical specifications are measured at  $V_{IN}$  = 7V to 42V,  $V_{OUT}$  = 1.2V,  $C_{L}V_{CC}$  = 10 $\mu$ F,  $T_{A}$  = +25°C. Boldface limits apply across the internal junction temperature range, -40°C to +125°C. (Continued)

| Parameter                                                   | Symbol                | Test Conditions                                      | Min<br>(Note 9) | Тур      | Max<br>(Note 9)     | Unit |

|-------------------------------------------------------------|-----------------------|------------------------------------------------------|-----------------|----------|---------------------|------|

| PGOOD Upper Threshold                                       | $V_{PGOV}$            |                                                      | 109.0           | 112.5    | 115.0               | %    |

| PGOOD Lower Threshold                                       | V <sub>PGUV</sub>     |                                                      | 85.0            | 87.5     | 92.0                | %    |

| PGOOD Low-Level Voltage                                     | $V_{PGLOW}$           | I_SINK = 2mA                                         |                 |          | 0.35                | V    |

| PGOOD Leakage Current                                       | I <sub>PGLKG</sub>    | PGOOD = 5V                                           |                 | 20       | 150                 | nA   |

| PGOOD Timing                                                |                       |                                                      |                 | I        |                     |      |

| V <sub>OUT</sub> Rising Threshold to PGOOD Rising (Note 11) | t <sub>PGR</sub>      |                                                      |                 | 1.1      | 5                   | ms   |

| V <sub>OUT</sub> Falling Threshold to PGOOD Falling         | t <sub>PGF</sub>      |                                                      |                 | 75       |                     | μs   |

| Reference Section                                           |                       |                                                      | -1              | ı        |                     |      |

| Internal Reference Voltage                                  | V <sub>REF</sub>      |                                                      |                 | 0.600    |                     | V    |

| Reference Voltage Accuracy                                  |                       | T <sub>A</sub> = 0°C to +85°C                        | -0.75           |          | +0.75               | %    |

|                                                             |                       | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -1.00           |          | +1.00               | %    |

| FB Bias Current                                             | I <sub>FBLKG</sub>    |                                                      | -40             | 0        | 40                  | nA   |

| PWM Controller Error Amplifiers                             | -                     | L                                                    | 1               | <u>I</u> | 1                   |      |

| Input Common-Mode Range                                     |                       | V <sub>IN</sub> = 12V                                | 0               |          | V <sub>CC</sub> - 2 | V    |

| DC Gain                                                     |                       | V <sub>IN</sub> = 12V                                |                 | 88       |                     | dB   |

| Gain-BW Product                                             | GBW                   | V <sub>IN</sub> = 12V                                |                 | 8        |                     | MHz  |

| Slew Rate                                                   | SR                    | V <sub>IN</sub> = 12V                                |                 | 2.0      |                     | V/µs |

| COMP V <sub>OL</sub>                                        |                       | V <sub>IN</sub> = 12V                                |                 | 0.4      |                     | V    |

| COMP V <sub>OH</sub>                                        |                       | V <sub>IN</sub> = 12V                                |                 | 2.6      |                     | V    |

| COMP Sink Current (Note 12)                                 |                       | V <sub>COMP</sub> = 2.5V                             |                 |          | 30                  | mA   |

| COMP Source Current (Note 12)                               |                       | V <sub>COMP</sub> = 2.5V                             |                 |          | 30                  | mA   |

| PWM Regulator                                               |                       | COMI                                                 | 1               |          |                     |      |

| Minimum Off-Time                                            | t <sub>OFF_MIN</sub>  |                                                      |                 | 308      | 412                 | ns   |

| Minimum On-Time (Note 12)                                   | t <sub>ON_MIN</sub>   |                                                      |                 | 40       | 60                  | ns   |

| Peak-to-Peak Sawtooth Amplitude                             | DV <sub>RAMP</sub>    | V <sub>IN</sub> = 20V                                |                 | 1.0      |                     | V    |

| ·                                                           | TOWN                  | V <sub>IN</sub> = 12V                                |                 | 0.6      |                     | V    |

| Ramp Offset                                                 |                       |                                                      |                 | 1.0      |                     | V    |

| Switching Frequency                                         |                       |                                                      | 1               |          |                     |      |

| Switching Frequency                                         | f <sub>SW</sub>       | RT PIN connect to SGND                               | 250             | 300      | 350                 | kHz  |

| Switching Frequency                                         |                       | RT PIN connect to VCC or FLOAT                       | 515             | 600      | 645                 | kHz  |

| Switching Frequency                                         |                       | $R_T = 36k\Omega$                                    | 890             | 1050     | 1195                | kHz  |

| Switching Frequency                                         |                       | $R_T = 16.5k\Omega$                                  | 1650            | 2000     | 2375                | kHz  |

| R <sub>T</sub> Voltage                                      | V <sub>RT</sub>       | $R_T = 36k\Omega$                                    |                 | 770      |                     | mV   |

| Synchronization                                             |                       | 1                                                    | _1              | <u>I</u> | I                   |      |

| SYNC Synchronization Range (Note 12)                        | F <sub>SYNC</sub>     | $R_T = 0\Omega$                                      | 354             |          | 1000                | kHz  |

| Diode Emulation Mode Detection                              | 20                    | 1                                                    |                 | I        | <u> </u>            |      |

| MOD/SYNC Threshold High (Note 12)                           | V <sub>MODETHH</sub>  |                                                      | 1.1             | 1.6      | 2.1                 | V    |

| MOD/SYNC Hysteresis (Note 12)                               | V <sub>MODEHYST</sub> |                                                      |                 | 200      |                     | mV   |

| Diode Emulation Phase Threshold (Note 10)                   | V <sub>CROSS</sub>    | V <sub>IN</sub> = 12V                                |                 | -3       |                     | mV   |

| Overvoltage Protection                                      |                       |                                                      | 1               | <u> </u> |                     |      |

Unless otherwise noted, typical specifications are measured at  $V_{IN}$  = 7V to 42V,  $V_{OUT}$  = 1.2V,  $C_{L}V_{CC}$  = 10 $\mu$ F,  $T_{A}$  = +25°C. **Boldface limits apply across the internal junction temperature range, -40°C to +125°C. (Continued)**

| Parameter                                                   | Symbol              | Test Conditions                                      | Min<br>(Note 9) | Тур  | Max<br>(Note 9) | Unit |

|-------------------------------------------------------------|---------------------|------------------------------------------------------|-----------------|------|-----------------|------|

| OVP Threshold                                               | V <sub>OVTH</sub>   |                                                      | 116             | 121  | 127             | %    |

| Overcurrent Protection                                      |                     |                                                      |                 |      |                 |      |

| OCP Threshold (Note 14)                                     | І <sub>ОСТН</sub>   | R <sub>OCSET</sub> resistor open, at +125°C junction |                 | 19.4 |                 | Α    |

| Over-Temperature                                            |                     |                                                      |                 |      |                 |      |

| Over-Temperature Shutdown (Controller Junction Temperature) | T <sub>OT-TH</sub>  |                                                      |                 | 150  |                 | °C   |

| Over-Temperature Hysteresis                                 | T <sub>OT-HYS</sub> |                                                      |                 | 15   |                 | °C   |

#### Notes:

- In normal operation, where the device is supplied with voltage on the VIN pin, the VCC pin provides a 5V output capable of sourcing 75mA (minimum). This is the total shutdown current with V<sub>IN</sub> = 7V and 42V.

- Operating current is the supply current consumed when the device is active but not switching. It does not include gate drive current.

- 9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. Controller is independently tested prior to module assembly.

- 10. Threshold voltage at PHASE pin for turning off the bottom MOSFET during DEM.

- When soft-start time is less than 4.5ms, t<sub>PGR</sub> increases. With internal soft-start (the fastest soft-start time), t<sub>PGR</sub> increases close to its maximum limit 5ms.

- 12. Compliance to limits is assured by characterization and design.

- 13. Maximum limit 100% production tested up to 5V.

- 14.  $V_{IN}$  = 24V,  $V_{OUT}$  = 3.3V at 125°C junction.

# 3. Typical Performance Curves

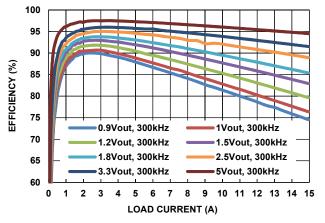

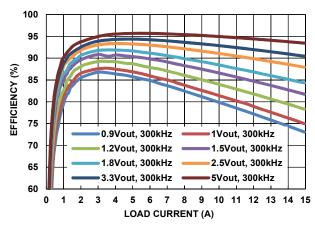

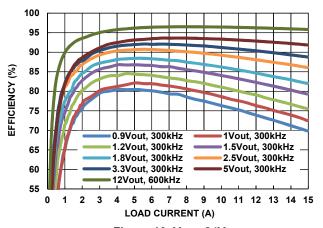

#### 3.1 Efficiency Performance

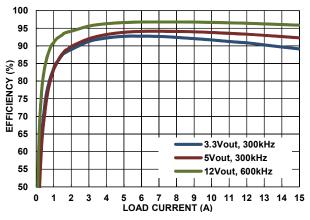

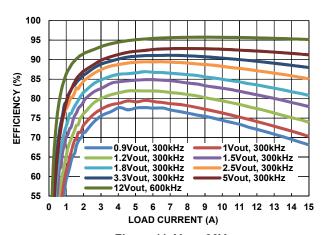

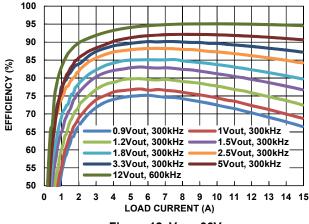

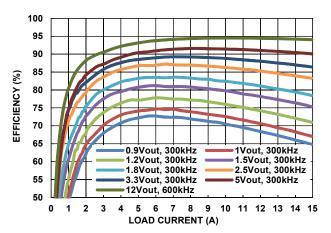

Operating condition:  $T_A = +25$ °C, no air flow. Device in PWM mode. Typical values are used unless otherwise noted.

Figure 8. V<sub>IN</sub> = 7V

Figure 9. V<sub>IN</sub> = 12V

Figure 10. V<sub>IN</sub> = 24V

Figure 11. V<sub>IN</sub> = 30V

Figure 12. V<sub>IN</sub> = 36V

Figure 13. V<sub>IN</sub> = 42V

#### 3.2 Output Voltage Ripple

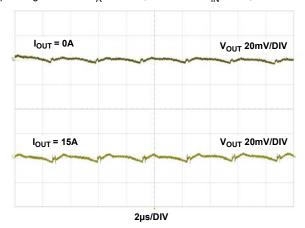

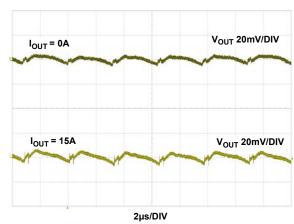

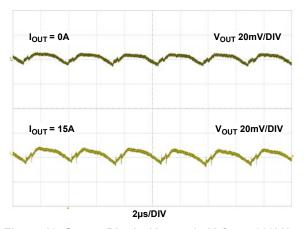

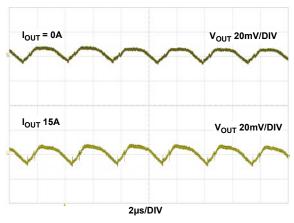

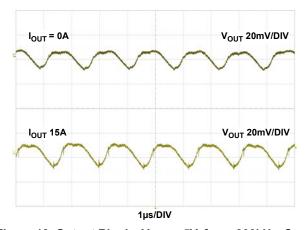

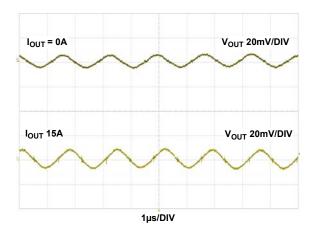

Operating condition:  $T_A = +25$ °C, no air flow.  $V_{IN} = 24$ V, CCM mode. Typical values are used unless otherwise noted.

Figure 14. Output Ripple,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 300kHz$ ,  $C_{OUT} = 4x100\mu F$  Ceramic +  $1x470\mu F$  POSCAP

Figure 15. Output Ripple, V<sub>OUT</sub> = 1.8V, f<sub>SW</sub> = 300kHz, C<sub>OUT</sub> = 4x100μF Ceramic + 1x470μF POSCAP

Figure 16. Output Ripple,  $V_{OUT}$  = 2.5V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 17. Output Ripple,  $V_{OUT}$  = 3.3V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 18. Output Ripple, V<sub>OUT</sub> = 5V, f<sub>SW</sub> = 300kHz, C<sub>OUT</sub> = 4x100µF Ceramic + 1x330µF POSCAP

Figure 19. Output Ripple,  $V_{OUT} = 12V$ ,  $f_{SW} = 600kHz$ ,  $C_{OUT} = 12x22\mu F$  Ceramic +  $2x150\mu F$  POSCAP

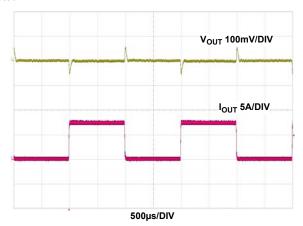

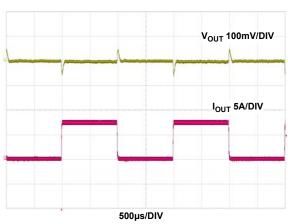

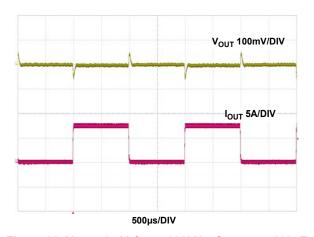

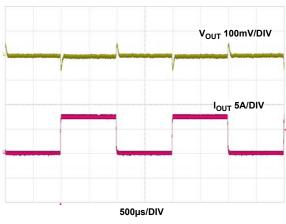

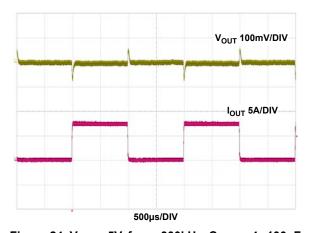

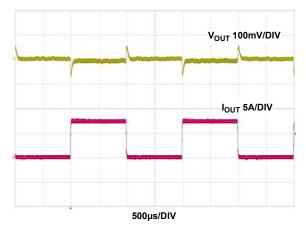

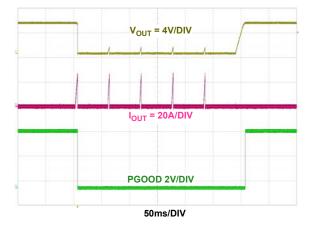

# 3.3 Load Transient Response Performance

Operating condition:  $T_A = +25$ °C, no air flow.  $V_{IN} = 24V$ , CCM mode, 0A - 7.5A,  $2.5A/\mu s$  step load. Typical values are used unless otherwise noted.

Figure 20.  $V_{OUT}$  = 1.2V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 21.  $V_{OUT}$  = 1.8V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 22.  $V_{OUT}$  =2.5V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 23.  $V_{OUT}$  = 3.3V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x470 $\mu$ F POSCAP

Figure 24.  $V_{OUT}$  =5V,  $f_{SW}$  = 300kHz,  $C_{OUT}$  = 4x100 $\mu$ F Ceramic + 1x330 $\mu$ F POSCAP

Figure 25.  $V_{OUT}$  = 12V,  $f_{SW}$  = 600kHz,  $C_{OUT}$  = 12x22 $\mu$ F Ceramic + 2x150 $\mu$ F POSCAP

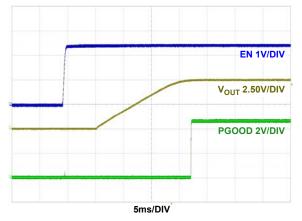

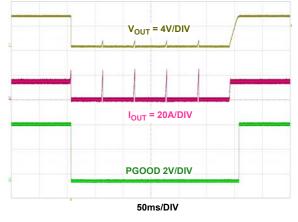

## 3.4 Start-Up Waveforms

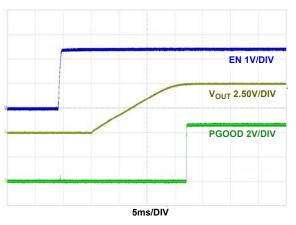

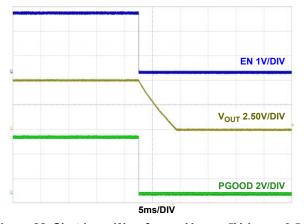

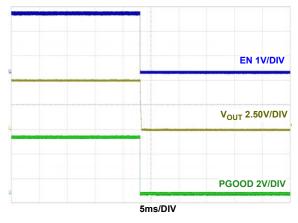

Operating condition:  $T_A = +25$ °C, no air flow.  $V_{IN} = 24$ V,  $f_{SW} = 300$ kHz,  $C_{OUT} = 4x100$ µF CERAMIC + 1x330µF POSCAP, CCM mode. Typical values are used unless otherwise noted.

Figure 26. Start-Up Waveforms;  $V_{OUT} = 5V$ ,  $I_{OUT} = 0A$ ,

Figure 27. Start-Up Waveforms; V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 15A

Figure 28. Shutdown Waveforms; V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 0.5A

Figure 29. Shutdown Waveforms; V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 15A

Figure 30. OCP Response; Output Short-Circuited from No Load to Ground and Released,  $V_{OUT} = 5V$ ,  $I_{OUT} = 0A$

Figure 31. OCP Response; Output Short-Circuited from 15A to Ground and Released, V<sub>OUT</sub> = 5V, I<sub>OUT</sub> = 15A

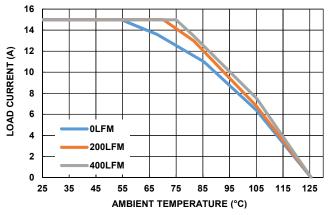

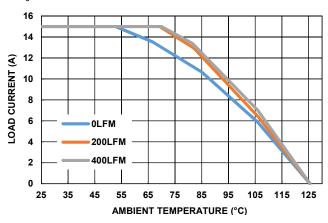

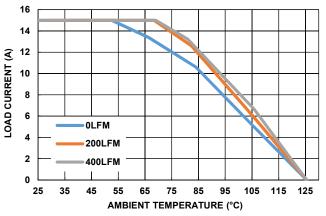

#### 3.5 Derating

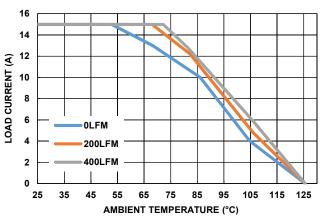

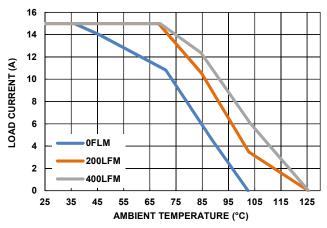

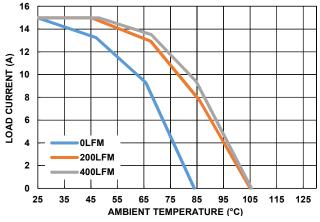

Operating condition:  $V_{IN}$  = 24V. All of the following curves were plotted at  $T_J$  = +120°C.

Figure 32. PWM/CCM Mode,  $V_{OUT} = 1.2V$ ,  $f_{SW} = 300kHz$

Figure 33. PWM/CCM Mode,  $V_{OUT}$  = 1.8V,  $f_{SW}$  = 300kHz

Figure 34. PWM/CCM Mode,  $V_{OUT} = 2.5V$ ,  $f_{SW} = 300kHz$

Figure 35. PWM/CCM Mode,  $V_{OUT}$  = 3.3V,  $f_{SW}$  = 300kHz

Figure 36. PWM/CCM Mode,  $V_{OUT} = 5V$ ,  $f_{SW} = 300$ kHz

Figure 37. PWM/CCM Mode,  $V_{OUT} = 12V$ ,  $f_{SW} = 600kHz$

## 4. Functional Description

#### 4.1 Power-Good Indicator

The power-good signal can be used to monitor the status of the output voltage for undervoltage and overvoltage conditions. This open-drain, PGOOD output is asserted whenever the output voltage is within ±12.5% of the selected target value. This voltage is measured through the feedback resistive divider hence referenced to the internal 0.6V reference. The PGOOD assertion occurs after a 1.1ms blanking delay upon the output voltage reaching the regulation window. PGOOD is deasserted without any delay when an output undervoltage or overvoltage is detected or when EN is pulled LOW.

#### 4.2 Self-Enable Operation

An internal pull-up resistor from EN to VCC allows for self-enabling operation. Leaving the EN pin floating enables the ISL8215M as soon as VIN reaches the UVLO threshold, at which point the soft-start circuitry is activated.

Figure 38. Self-Enable Operation

For operations in which the ISL8215M is required to turn on at a specific input voltage level, external circuitry must be implemented to control the voltage applied on the EN pin through a resistor divider. An optional zener (D1 as shown in Figure 39) may also be required to maintain the EN voltage within the recommended operating conditions.

Figure 39. 18V<sub>IN</sub> Minimum Self-Enable Operation

#### 4.3 Enable

Driving the EN pin high or low respectively enables or disables operations of the ISL8215M. When the EN pin voltage reaches 1.6V, an initialization of the ISL8215M internal circuit is performed. Pulling the EN low disables all internal circuitry to achieve a low standby current and discharges the SS/TRK pin to GND by an internal MOSFET with  $70\Omega \, r_{DS(ON)}$ .

#### 4.4 Prebiased Power-Up

The ISL8215M has the ability to soft-start with a prebiased output. The output voltage will not be pulled down during prebiased startup. PWM operations will initiate only when the soft-start ramp reaches the prebiased voltage times the resistive divider ratio. Overvoltage protection is active during soft-start operations.

Figure 40. Prebiased Power-Up Waveform, Prebiased Voltage = 3.0V, V<sub>OUT</sub> = 3.3V, I<sub>OUT</sub> = No Load

#### 4.5 PWM/CCM Mode

Tying the MOD/SYNC pin to signal ground or leaving it floating selects the PWM only mode of operation. In this mode, the ISL8215M operates at a constant frequency at all load currents. While this mode provides lower conversion efficiency at light current load, it may be sometimes required for applications sensitive to electromagnetic interferences.

#### 4.6 PSM/DEM Light-Load Efficiency Mode

Tying the MOD/SYNC pin to VCC selects the PSM/DEM enhanced light-load efficiency mode of operation. In this mode, the ISL8215M operates in high-efficiency Diode Emulation Mode (DEM) and Pulse Skipping Mode (PSM) at light-load conditions. The inductor current is not allowed to reverse (discontinuous operation) while at very light loads, and the ISL8215M enters the pulse skipping function. Although this mode provides increased conversion efficiency at light load, it also increases the output ripple voltage and operates at a non-constant frequency.

#### 4.7 Internal 5V Linear Regulator (V<sub>CC</sub>)

An internal low dropout regulator powers all ISL8215M internal circuitry allowing the device to operate from a single, wide-input voltage rail from 7V to 42V. For proper operation, the output of this internal LDO,  $V_{CC}$ , should be decoupled to power ground with a  $10\mu F$  capacitor positioned as close as possible to the pin. No other circuitry should be connected to VCC.

## 4.8 Gate Control Logic Optimization

The ISL8215M implements a specific proprietary MOSFET gates control logic that optimizes the performance over a wide range of operating conditions. This circuitry provides adaptive dead time control by monitoring the real gate waveforms of both the high-side and low-side MOSFETs. A shoot-through control logic provides a 16ns dead time to ensure that both the upper and lower MOSFETs will not turn on simultaneously and cause a shoot-through condition.

# 5. Application Information

#### 5.1 Output Voltage Programming

The ISL8215M supports an adjustable output voltage range of 0.6V to 12V. A single resistor,  $R_2$ , placed from FB to SGND sets the output voltage according to (EQ. 1).

(EQ. 1)

$$R_2 = \frac{(R_1 \times 0.6)}{(V_{OUT} - 0.6)}$$

where  $R_1$  = Fixed high-side resistor value of 43.2k $\Omega$  ±1% tolerance inside the module and  $R_2$  = Resistor connected from FB to SGND in k $\Omega$ .

<u>Table 3</u> assists in selecting the value of resistor  $R_2$  for typical output voltages. For maximum output voltage accuracy,  $R_2$  should be selected with a tolerance of 0.1% or better.

| V <sub>OUT</sub><br>(V) | R <sub>2</sub><br>E192 Series |  |

|-------------------------|-------------------------------|--|

| 0.6                     | Open                          |  |

| 0.8                     | 130kΩ                         |  |

| 0.85                    | 104kΩ                         |  |

| 0.90                    | 86.6kΩ                        |  |

| 0.95                    | 74.1kΩ                        |  |

| 1.0                     | 64.9kΩ                        |  |

| 1.1                     | 51.7kΩ                        |  |

| 1.2                     | 43.2kΩ                        |  |

| 1.5                     | 28.7kΩ                        |  |

| 1.8                     | 21.5kΩ                        |  |

| 2.5                     | 13.7kΩ                        |  |

| 3.3                     | 9.53kΩ                        |  |

| 5                       | 5.90kΩ                        |  |

| 12                      | 2.26kΩ                        |  |

**Table 3. Output Voltage Resistor Settings**

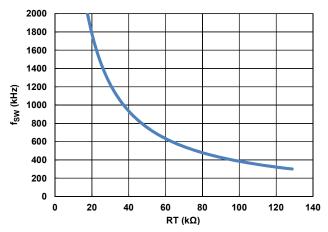

## 5.2 Switching Frequency Selection

The switching frequency of the ISL8215M is programmable from 300kHz to 2MHz typical and is set by a resistor connected from the RT pin to SGND according to (EQ. 2):

$$(\text{EQ. 2}) \hspace{1cm} R_{T} = \Big(\frac{39.2}{f_{SW}} - 1.96\Big) k\Omega$$

where f<sub>SW</sub> is the switching frequency in MHz.

The switching frequency can be set to 300 kHz when the RT pin is tied to ground. The switching frequency can be increased to 600 kHz if the RT pin is tied to VCC or left floating. Switching frequency selection is a trade-off between efficiency, output voltage ripple, and load transient response requirements. Typically, a low switching frequency improves efficiency by reducing MOSFET switching losses while a high switching frequency improves the output voltage ripple and transient response in conjunction with the value and type of the output capacitance. The frequency setting curve shown in Figure 41 assists in selecting the correct value for the resistor  $R_T$ .

Figure 41. R<sub>T</sub> vs Switching Frequency f<sub>SW</sub>

When using the ISL8215M internal oscillator to control switching operations, the desired control scheme must be configured. In this mode, the MOD/SYNC pin selects the required configuration.

#### 5.3 External Frequency Synchronization

The ISL8215M can be synchronized to an external clock applied on the MOD/SYNC pin. The external clock should be a square pulse waveform with a frequency in the range of 354kHz - 1MHz. The programmed frequency of the ISL8215M module, which is set by the resistor connected to the RT pin should be lower than the external clock frequency. The duty cycle of the external clock should be within 30% to 70% (typically 50%), while the amplitude should be in the range of 3V to 5V.

To ensure proper operation, the external clock frequency must be at least 18% higher than the programmed default frequency of the module. The module should be disabled before turning off the external clock. When frequency synchronization is in effect, the ISL8215M operates in forced PWM mode across all loads.

#### 5.4 Soft-Start Operation

The ISL8215M provides soft-start operations for applications where inrush current during startup need be reduced.

A soft-start capacitor placed between the SS/TRK pin and signal ground adjusts the soft-start output voltage ramp rate. The typical soft-start time is based on the soft-start capacitor value and set according to (EQ. 3):

(EQ. 3)

$$t_{SS} = 0.6V \left(\frac{C_{SS}}{2}\right)$$

where  $C_{SS}$  is in nF and  $t_{SS}$  in ms.

The soft-start time setting curve shown in <u>Figure 42</u> assists in selecting the correct value for the capacitor  $C_{SS}$ . When the soft-start time set by external  $C_{SS}$  or tracking is less than 1.5ms, an internal soft-start circuitry of 1.5ms will take over the soft-start function. Furthermore, overvoltage protection is active during soft-starting operation.

Figure 42. C<sub>SS</sub> vs t<sub>SS</sub>

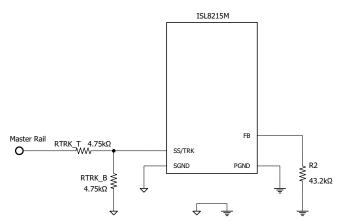

## 5.5 Tracking Operation

The ISL8215M can be configured to track an external supply, either coincidently or ratiometrically. To implement this functionality, a tracking resistor divider is connected between the external supply output (Master rail) and ground. The center point of this resistor divider is connected to the SS/TRK pin of ISL8215M.

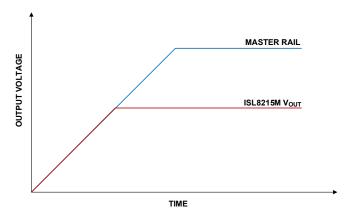

Figure 43. ISL8215M V<sub>OUT</sub> = 1.2V - Coincidental Tracking of Master Rail - Divider Ratio of 1:1

Coincident tracking is achieved when both the master rail and ISL8215M output rail reach their respective regulation voltage levels with the same slope. As shown in Figure 44, the master rail and the ISL8215M output rail reach regulation at two different times. Coincident tracking can be achieved by setting the external resistor divider ratio (RTRK\_T/RTRK\_B) equal to the feedback resistor divider ratio ( $R_1/R_2$ ) of the ISL8215M. Table 3 on page 21 can assist in selecting the appropriate resistor value for different output voltages.

Figure 44. Coincidental Tracking of Master Rail

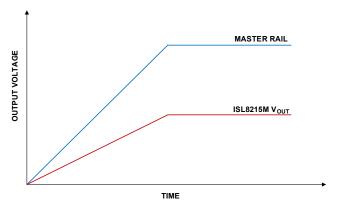

Ratiometric tracking is achieved when the master rail and the ISL8215M output rail both reach their final regulation value at the same time but with different slopes, as shown in <u>Figure 45</u>. Use <u>(EQ. 4)</u> to calculate the resistor divider ratio (RTRK T/RTRK B) to implement ratiometric tracking.

$$(EQ. 4) V_{Master rail} \times \frac{RTRK\_B}{RTRK\_B + RTRK\_T} = 0.6$$

Note that R1 is a fixed high-side resistor of value  $43.2k\Omega$ .

When the voltage at the SS/TRK pin reaches ~550mV, the output voltage is decided by the internal reference of the ISL8215M controller. In addition, the tracking resistor divider of the master rail should include resistors of values less than  $10k\Omega$  to minimize the impact of the  $2\mu$ A soft-start current on the tracking function.

Figure 45. Ratiometric Tracking of Master Rail

### 5.6 Input Voltage Range

The ISL8215M is designed to operate from a single wide input supply ranging from 7V DC to 42V DC. Limitations on the minimum on-time and minimum off-time required by the ISL8215M limit the minimum and maximum conversion ratios, or duty cycles, supported. By extension, the supported input voltage range for a selected output voltage and selected operating frequency may be effectively reduced.

The maximum input voltage is limited by the minimum on-time  $(t_{ON(min)})$  as shown in (EQ. 5).

(EQ. 5)

$$V_{IN(max)} \le \left(\frac{V_{OUT}}{t_{ON(min)} \times f_{SW}}\right)$$

where  $t_{ON(min)} = 60$ ns worst case and  $f_{SW}$  is the switching frequency in Hz.

The minimum input voltage is limited by the minimum off-time ( $t_{OFF(min)}$ ), ON-resistance of the high-side FET,  $r_{DS(ON)}$ , series resistance of the inductor ( $R_L$ ), and the load current ( $I_{OUT}$ ) as shown in (EQ. 6). Because of the temperature coefficient of the MOSFET and inductor, note that the minimum value of  $V_{IN}$  will occur at the +125°C at  $R_L$  = 9.7m $\Omega$  and  $r_{DS(ON)}$ = 18.75m $\Omega$ .

(EQ. 6)

$$V_{IN(min)} \ge \left( \frac{V_{OUT} + I_{OUT} \times (r_{DS(ON)} + R_L)}{1 - t_{OFE(min)} \times f_{SW}} \right)$$

where  $t_{OFF(min)} = 412$ ns worst case.

#### 5.7 Input Capacitor Selection

The important parameters for the input capacitor(s) are the voltage rating and the RMS current rating. For reliable operation, select input capacitors with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and 1.5 times is a conservative guideline. The  $AC_{RMS}$  input current varies with the load given in (EQ. 7):

(EQ. 7)

$$I_{RMS} = \sqrt{D(1-D)} \cdot I_{OUT}$$

Where D is duty cycle of the PWM.

The maximum RMS current supplied by the input capacitance occurs at  $V_{IN} = 2 \times V_{OUT}$ , D = 50% as shown in (EQ. 8):

(EQ. 8)

$$I_{RMS} = \frac{1}{2} \cdot I_{OUT}$$

Refer to the capacitor vendor to check the RMS current rating. It should be noted that the current rating is decided by the ambient temperature or temperature rise. Each 1210 size 10µF low ESR capacitor is typically good for 2A to 3A RMS ripple current.

Use a mix of input bypass capacitors to control the voltage stress across the MOSFETs. Use ceramic capacitors for the high frequency decoupling and bulk capacitors to supply the RMS current. Small ceramic capacitors can be placed very close to the MOSFETs to suppress the voltage induced in the parasitic circuit impedances.

Solid tantalum capacitors can be used, however, caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge current at power-up.

#### 5.8 **Output Capacitor Selection**

The ISL8215M is designed for low output voltage ripple. In general, output capacitors should be selected to meet the dynamic regulation requirements including ripple voltage and load transients, which can be met with bulk output capacitors that have adequately low ESR and ESL.

High frequency capacitors initially supply the transient current and slow the slew rate of load transient seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR and ESL and voltage rating requirements, as well as actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low ESR/ESL components. Consult with the manufacturer of the load circuitry for specific decoupling requirements.

Use only specialized low ESR capacitors intended for switching regulator applications for the bulk capacitors. In most cases, multiple small case electrolytic capacitors perform better than a single large case capacitor.

In conclusion, the output capacitors must meet the following criteria:

- (1) They must have sufficient bulk capacitance to sustain the output voltage during a load transient while the output inductor current is slewing to the value of the load transient.

- (2) The ESR must be sufficiently low to meet the desired output voltage ripple due to the output inductor current. The recommended output capacitor value for the ISL8215M is between 400µF to 1000µF. See Tables 1 and 2 on page 9 for more capacitor information. All ceramic capacitors are possible with loop analysis to ensure stability.

ISL8215M 6. Protection Circuits

## 6. Protection Circuits

## 6.1 Undervoltage Lockout

The ISL8215M includes UVLO protection, which keeps the device in a reset condition until a proper operating voltage is applied. It also shuts down the ISL8215M if the operating voltage drops below a predefined value. Upon assertion of the UVLO state, the controller is completely disabled. PGOOD is valid and will be deasserted.

#### 6.2 Overcurrent Protection

The ISL8215M uses the lower MOSFET's ON-resistance,  $r_{DS(ON)}$ , to monitor the current in the converter. The sensed voltage drop across the MOSFET's drain-to-source is compared to a threshold voltage set by the resistor,  $R_{OCSET}$ , connected from the OCS pin to ground. Because  $r_{DS(ON)}$  is higher at hot temperatures and lower at cold temperatures, the OCP setpoint at room and cold temperatures will be higher than the OCP setpoint at hot temperatures.

For applications involving less than 15A load, it is recommended to further reduce the OCP setpoint to improve the system reliability, and (EQ. 9) can be used to calculate the value of the OCP set resistor.

(EQ. 9)

$$R_{OCSET} = \frac{(26.1 \cdot R_{Nom} \cdot (I_O/15))}{(R_{Nom} \cdot (1 - (I_O/15)) + 26.1)} k\Omega$$

where,

$I_O$  = Desired full load current (A).

$R_{OCSET}$  = Resistor connected to the OCS pin (k $\Omega$ ).

$R_{Nom} = R_{OCSET}$  resistor to ensure 15A full load operation (k $\Omega$ ).

R<sub>OCSET</sub> values for ensuring 15A full load operation:

- 20M $\Omega$  for 3.3V output and below (simulating a "Do Not Populate" (DNP) condition).

- $205k\Omega$  for 5V output

- $118k\Omega$  for 12V output

In (EQ. 9) the typical load current to hit OCP at  $+120^{\circ}$ C is set to around 20% higher than the desired full load current. The 20% margin is due to the controller OCP and the MOSFET  $r_{DS(ON)}$  tolerance.

If an overcurrent is detected, the upper MOSFET remains off and the lower MOSFET remains on until the next cycle. As a result, the converter skips a pulse. When the overload condition is removed, the converter resumes normal operation. If an overcurrent is detected for two consecutive clock cycles, the module enters Hiccup mode by turning off the gate driver and entering soft-start. The ISL8215M stays off for 50ms before trying to restart and continues to cycle through soft-start until the overcurrent condition is removed. Hiccup mode is active during soft-start, so ensure that the peak inductor current does not exceed the overcurrent threshold during soft-start.

When OCP is triggered, the SS/TRK pin is pulled to ground by an internal MOSFET for hiccup restart. When configured to track another voltage rail, the SS/TRK pin rises up much faster than the internal minimum soft-start ramp. The voltage reference is then clamped to the internal minimum soft-start ramp. Thus, smooth soft-start hiccup is achieved even with the tracking function.

ISL8215M 6. Protection Circuits

#### 6.3 Overvoltage Protection

The overvoltage set point is set at 121% of the nominal output voltage set by the feedback resistors. In case of an overvoltage event, the module will attempt to bring the output voltage back into regulation by keeping the upper MOSFET turned off and the lower MOSFET turned on. If the overvoltage condition has been corrected and the output voltage returns to 110% of the nominal output voltage, both high-side and low-side MOSFETs will be turned off until the output voltage drops to the nominal voltage to start work in normal PWM switching.

#### 6.4 Over-Temperature Protection

The IC incorporates an over-temperature protection circuit that shuts down the IC when a die temperature of  $+150^{\circ}$ C is reached. Normal operation resumes when the die temperature drops below  $+145^{\circ}$ C through the initiation of a full soft-start cycle. During OTP shutdown, the IC consumes only  $100\mu$ A current. When the controller is disabled, thermal protection is inactive. This helps achieve a very low shutdown current of  $5\mu$ A.

ISL8215M 7. Layout Guidelines

## 7. Layout Guidelines

Careful attention to layout requirements is necessary for successful implementation of an ISL8215M based DC/DC converter. The ISL8215M switches at a very high frequency and, therefore, the switching times are very short. At these switching frequencies, even the shortest trace has significant impedance. Also, the peak gate drive current rises significantly in an extremely short time. Transition speed of the current from one device to another causes voltage spikes across the interconnecting impedances and parasitic circuit elements. These voltage spikes can degrade efficiency, generate EMI, and increase device overvoltage stress and ringing. Careful component selection and proper PC board layout minimize the magnitude of these voltage spikes.

#### 7.1 Layout Considerations

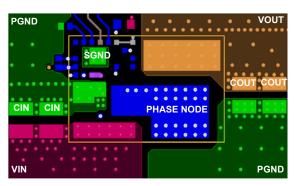

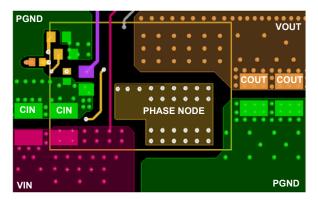

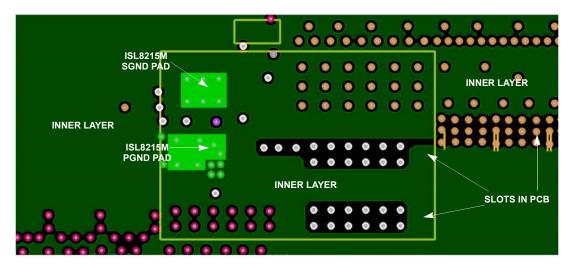

- (1) Place the input capacitors and high frequency decoupling ceramic capacitors between VIN and PGND, as close to the module as possible. The loop formed by the input capacitor, VIN pad, and PGND must be as small as possible to minimize the high frequency noise. The output capacitors should be placed close to the load. Use short, wide copper planes to connect the output capacitors to the load for avoiding any parasitic inductances and resistances. An illustrative layout example is shown in Figures 46 and 47.

- (2) VIN, VOUT, and PGND should use large copper planes to minimize conduction loss and thermal stress. Use enough vias to connect the power planes in different layers.

- (3) Use full ground planes in the internal layers (underneath the module) with shared SGND and PGND to simplify the layout design. It is recommended to use slots, as shown in <u>Figure 48 on page 29</u> to ensure that the switching current avoids the SGND pad of the module. It is recommended to use as much GND plane as possible for the layer directly above the bottom layer (containing components like input caps, output caps, etc). Use the top and bottom layer to route EN, VCC, and PGOOD signals.